作者:徐祥祯(义守大学机械与自动化工程学系副教授)

前言

电子构装(Electronic Packaging),主要是利用固定粘着技术,将集成电路(Integrated Circuit, IC)芯片固定在承载衬垫(Die Pad)上,并利用细微连接技术,引出电力讯号,并以绝缘材料予以密封,建构成立体结构。这种技术在上一世纪称为IC封装,由于电子产品种类越来越多且技术范围涵盖物理、化学、材料、机械、电机等学门,广义上说,将电子组件与芯片承载衬垫固定连接,装配成完整的系统或设备,以发挥IC原始设计功能的技术,即可称为电子构装。电子构装的功能,包含了以下几项(1)电源供应(2)信号传输(3)热量排除(4)保护支撑。

以微电子的制程而言,电子构装属于产品后段的制程技术,电子产品朝向轻薄短小趋势发展,IC芯片缩小但IO数增加、组件密度集中使功率提高,所产生热源如何排除问题,与来自构装制程所产生的残余应力,以及芯片在运作时各种材料间热膨胀系数差异所产生的热应力,此外,还有高分子材料因吸湿所引发的湿气膨胀应力。各种因温度、湿气引发的应力作用,导致构装材料间的分层、崩裂,或是芯片的破损,使得IC运作失效,造成可靠度问题。因此,电子构装技术开发的重要性,其实并不亚于前段的IC制程技术或其它微电子制程技术。

一、电子构装技术层次与分类

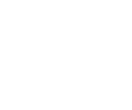

一般而言,电子构装技术因制程技术不同而区分成不同的层次,如图一所示。

第0层次的构装,是指直接在IC芯片上的连线制程,称为 Wafer Level;

第1层次的构装,是将IC芯片粘接于一构装体中并完成电路连线与密封保护,称为Module Level;

第2层次的构装,是指将第一层次构装完成的数个组件组合在 PCB电路板上,称为 Board Level;

第3层次的构装,则指将数个电路板组合于一主板 (Mother Board)上,称为 Card Level;

第4层次的构装,则为将数个主板组合成为电子产品,称为 Gate Level;

第5层次的构装,是指将将数个电子产品透过网路组合起來,称为 Network Level。

另外,将 IC芯片直接固定在 PCB上的Chip on Board技术,分类为第 1.5层次的构装。

图一 电子构装技术层次示意图

二、电子构装结构分析

电子构装的可靠度(Reliability),主要是探讨其故障机制(Failure Mechanism),大致上分为下列三种:

(1)热机械故障,这是由于温度增加造成构装内部材料因彼此间热膨胀系数不同产生热变形与热应力,最常见的热机械故障是断裂,断裂会导致芯片破裂、基板分离、填充物破裂、焊锡点疲劳。断裂的机制有脆性断裂及延性断裂。

(2)化学故障,这包含了化学腐蚀与金属扩散,当金属与水气或酸接触会产生腐蚀。高分子材料本身就会吸湿,而且与金属间不能完全密合,空气的湿气会扩散或以毛细作用传入构装体内,造成金属及焊线的腐蚀,残余湿气在高温作用会造成爆米花效应。此外,两种不同金属之间扩散,形成介金属化合物(Inter-Metallic Compound,IMC),造成金属的脆化并且减弱其降伏应力,如焊锡点破裂。

(3)电气故障,包含电迁移与静电放电,因IC芯片内电流密度高,电子在铝线移动将铝原子挤出,称为电迁移,造成导体线路电流不连续形成开路故障,与相邻导体形成短路故障。静电放电是指外界如人体或仪器设备的电荷经过放电途径,瞬间大量的电流进入IC芯片,造成电子组件故障。

电子构装的结构分析,简单的说是要预估结构体在承受某种负载(温度、湿度、压力、电气或是瞬间的外力作用)下的反应情形,计算结构体内部应力分布与变形量,或是算出结构体震动的固有频率,或是找出结构体热源所在以及散热途径等等,用来分析结构体的故障机制,提升电子构装的可靠度。因此,电子构装的结构分析所需技术知识范围,包含了固体力学(弹性、塑性、振动、光弹)、热机力学(热传学、材料力学)、破坏力学、材料科学等,相当广阔。任何新的电子产品的研发,都需要在形状、尺寸、材料、负荷、可靠与价格上作反复的结构分析。此外,电子产品在不能达到预期的功能或故障时,必须作多项的结构分析,以正确指出失效的原因,同时验证其量测值。不论是新创或是改良,工程师首先必须对整体结构有所了解;其次必须对结构体内的每一组件,分析其所受的负载,并运用这些力学原理求解。一旦确定后,工程师会依照结构体所需的强度及各材料的机械性质,来选择适当之尺寸。“构装”一词中,隐含了“结构分析”的意义,因此,将「IC封装」更名为「电子构装」,在学术界上有其意义存在。

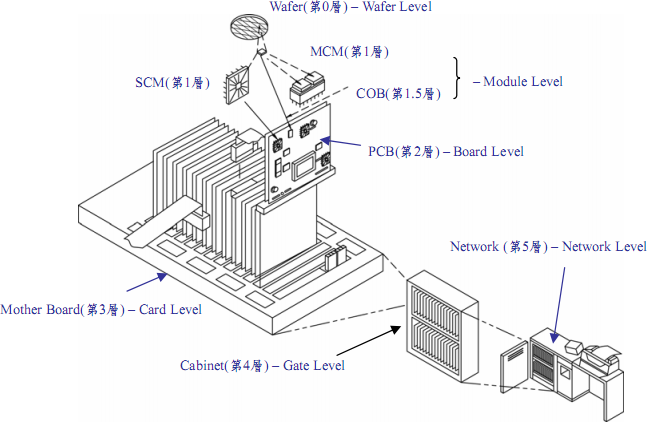

图二 PBGA(Plastic Ball Grid Array)构装结构示意图

一个典型的半导体构装PBGA结构的示意图,如图二所示。此构装材料使用了环氧树脂封胶(Epoxy Mold Compound)、芯片(Chip)、芯片接合剂(Die Attach)、金线(Au Wire)、基板(Substrate)、绿漆(Solder Mask)、导通孔(Via)、焊锡(Solder)。在封装过程中,因为反复进行加热、冷却,因各材料因热膨胀系数不同,在界面产生热应力而导致变形、裂缝、破坏。因为环保意识抬头,绿色构装(green package)需要无铅成份的焊锡、无卤素成分的环氧树脂封胶等,材料的改变会改变制程,其可靠度也跟着会改变,需要更多的测试与结构分析来验证。了解电子构装不同材料,如金线、铜箔、银膏、焊锡、硅芯片、环氧树脂封胶、基板、芯片接合剂、绿漆的材料特性,对于结构分析有很大的帮助。

由于有限元素分析(Finite Element Analysis,FEA)已广泛使用在工程上的结构分析与热分析上,并普遍被学术与产业研发所接受。在电子构装结构分析上,多重物理场偶合(Multi-physics)之FEA软件包被使用最为广泛。FEA仿真预测要精准,必须结构体内部全部材料要有正确的机械、热、电气性质以及适当的边界条件的设定,如牵涉到非线性求解,更需要有一个合适求解器(Solver)及解题顺序。因篇幅关系,仅就电子构装结构分析的部份FEA仿真预测结果作一示范说明:

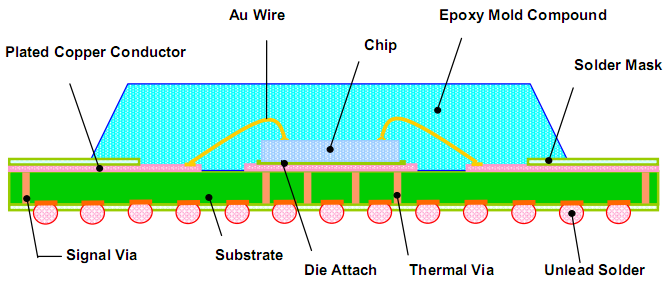

(一)热引发变形(Thermal-induced displacement)

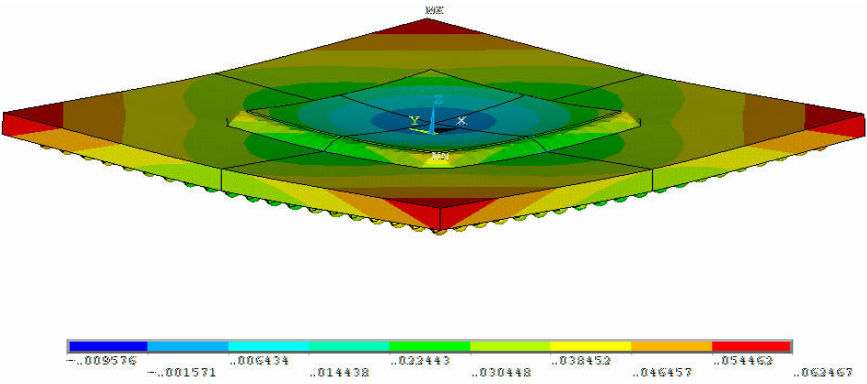

图三显示flip chip BGA(FCBGA)结构体的示意图,受热后所产生的内部变形(in-plane displacement)与Moiré Interferometry云纹干涉实验结果,以及热翘曲(thermal-induced warpage)预测。FEA预测结果与Moiré实验量测值的误差不到0.3%,显示FEA预测非常精确。

图三(a) FEA预测水平方向变形量(100oC降温到25oC)

图三(b) Moiré云纹干涉实验量测水平方向变形量(100oC降温到25oC)

图三(c) FEA预测翘曲(warpage)变形量(25oC加温到250oC)

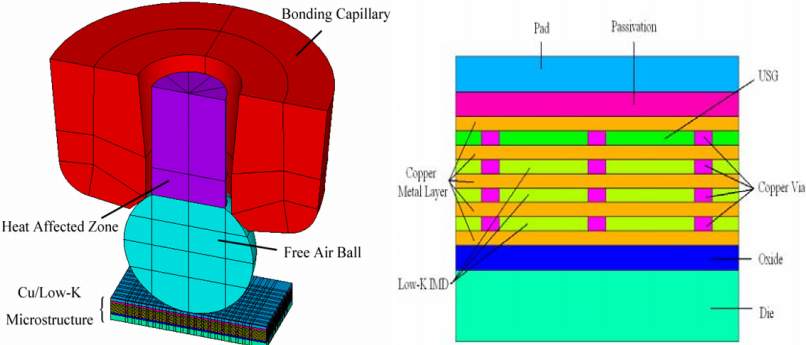

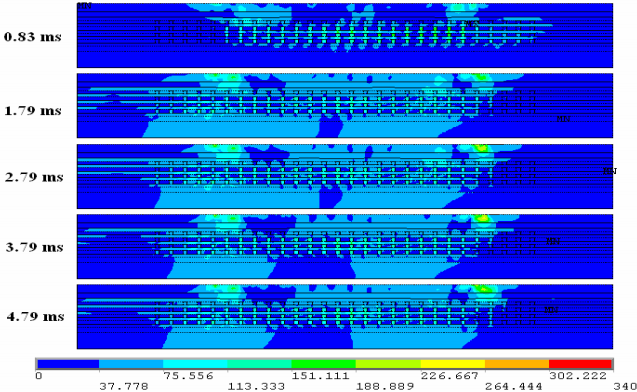

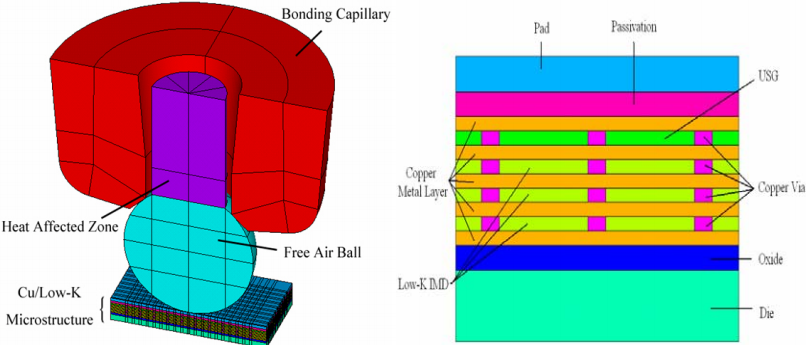

(二)焊线制程第一焊点模拟(Cu/low-K underlay microstructure dynamic response)

焊线(wire bonding)制程中,第一焊点(first bond)的制程相当复杂,制程上的参数bond force、bond speed、超音波USG的bond power需要转换成FEA的相关边界条件,制程温度与焊线上FAB及HAZ区域的机械性质要能反应到金线的材料性质上,更重要的是FEA模式要能仿真动态接触大变形的非线性行为。在此结构分析下,亦能正确的预测bond pad底下Cu/low-k微结构的应力波传递及破坏机制。而黄金价格飙涨,焊线以铜线取代金线,也是未来电子构装技术发展趋势之一。铜线的应变硬化在FEA模式中又必须充分的考虑进去。

图四(a)焊线制程第一焊点3维FEA模型 (b)Cu/low-K微结构示意图

图四(c) 预测热超音波制程的Cu/low-K微结构等效应力

(三)系统级封装焊锡之温度循环测试(Thermal cycle test for System-in-Package)

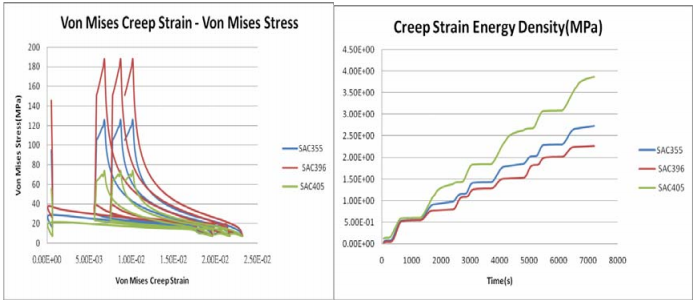

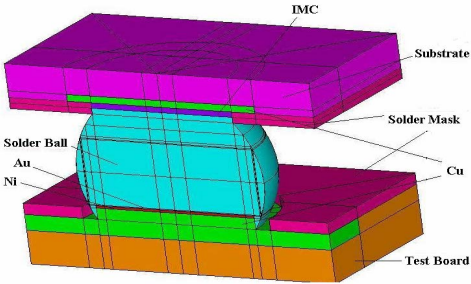

在绿色构装需求无铅焊锡,目前业界大多以锡银铜(Sn-Ag-Cu,SAC)合金来制作各式BGA的锡球,提供第二层次构装上板(board level)的表面粘着。因为SAC各合金材料比例不同,其机械性质不同,而铜的活性高、易扩散,生成金属间化合物,使结构变脆。当进行温度循环测试,从-40OC到125OC,包含加温、持温、降温、持温,温度往复的变化使结构受到往复的压缩、膨胀,SAC焊锡会产生疲劳破坏。而SAC焊锡的熔点约480K-520K间,当工作温度到其熔点一半时240K-260K,SAC焊锡会有潜变(creep)发生。因此在结构分析,就要选择具粘弹性行为的FEA元素,材料性质也必须反应潜变形为,而3D实体模型耗费太多计算机资源,因此使用slide model,又利利用圣维南原理,以子模型(sub-model)来作焊锡点附近的应力应变分析。在疲劳寿命预测,不同模式需要creep shear strain、creep von Mises stress-strain、以及creep strain energy density来代入不同模式。

图五(a)系统级封装3维FEA模型 (b)焊锡点子结构FEA模型

图五(c)焊锡点等效应变-等效应力图 (d)焊锡点子结构潜变应变能密度-时间图

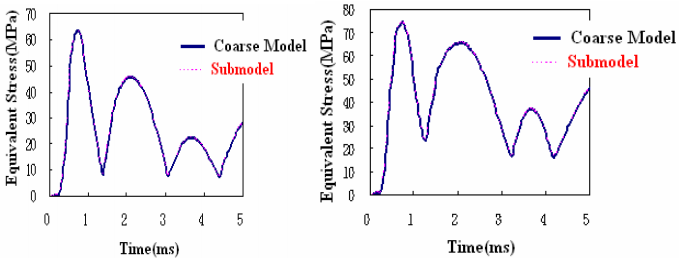

(四)系统级封装焊锡点掉落测试(Drop test using support excitation scheme)

焊锡点的另一个可靠度,就是上板后的电子产品要通过掉落测试(drop test)。在JEDEC掉落测试标准中加速度G值与sin波时间图,必须反应到求解顺序中。而边界条件中,则运用input D及support excitation方式,进行掉落测试模拟。由于金属扩散产生介金属化合物,使结构变脆,各种材料的机械性质必须正确的反应。延性破坏与脆性断裂准则(criteria)用在不同的结构与材料,破坏位置亦是研究重点之一。SAC锡球合金的比例、各结构的尺寸,用来作最优化的设计。

图六(a)系统级封装焊锡点3维子结构FEA模型

图六(b)焊锡点上方等效应力-时间图 (c)焊锡点下方等效应力-时间图

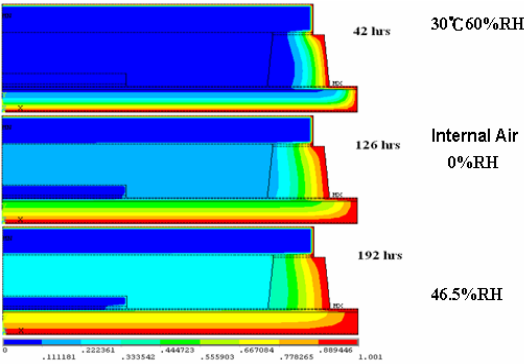

(五)CMOS影像传感器热-湿-固耦合(Thermo-hygro-mechanical effects for CIS)

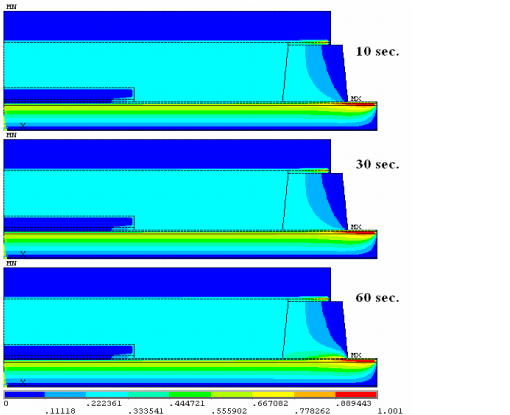

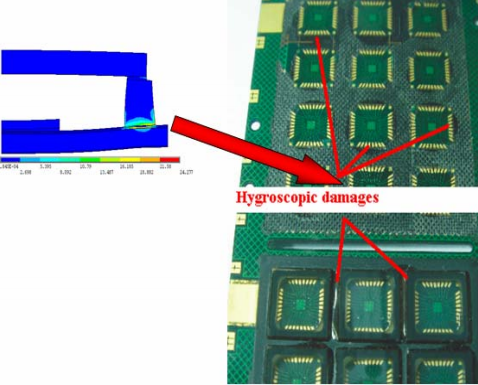

湿度所引发的电子构装可靠度问题,除了材料的湿气(moisture)性质,与湿气扩散系数(moisture diffusivity)不容易求得外,吸湿膨胀系数(coefficient of moisture expansion)也很难直接量测出来。在以往,工程师经常直接以烘烤来去湿,而FEA软件并不能直接仿真湿气分布与预测吸湿膨胀所产生的应力。由于湿气扩散原理与热传导的热传播原理一样,运用费肯第二扩散原理(Fick’s second diffusion law),推导出饱和吸湿系数、扩散系数、吸湿重量之间的关系式;在IR-Reflow过程中以Arrhenius方程式找到其活化能、扩散系数(此时,扩散系数会与温度相依);在吸湿膨胀所产生的应变,会等于残余湿度与吸湿膨胀系数之乘积。在FEA吸湿模拟中,密度(density)设定为1、热传导系数设为扩散系数乘以饱和吸湿系数、比热设为饱和吸湿系数,结构体外部边界的湿度全部设定成1与内部全部设为0,并进行瞬态非线性分析,所得的场变量即为湿度(wetness)。其次,进行IR-Reflow去湿过程的模拟,要注意的是,要将结构体全部边界设定为0。最后将残余的湿气与吸湿膨胀系数,以及因温度增加所产生的热变形,共同代入热湿-固耦合结构分析,得到构装整体的应力分布。

图七(a)QFN CMOS影像传感器吸湿192小时(30oC/60%RH)

图七(b)QFN CMOS影像传感器去湿60秒(30oC/60%RH)

图七(c)QFN CMOS影像传感器热-湿-结构偶合分析与基板失效图

三、结论

电子产品的趋势是轻薄短小,IC芯片也跟随着朝向高密度电子电路与多IO脚数发展。从过去的历程来看,要开发新产品,电子构装需要新技术、新制程、新材料的配合,还要有新机台的改善。在开发流程上,大多以FEA仿真来预测构装结构体在各种环境的可靠度来进行设计或改改,再配合参数设计,以测试实验数据验证。无论电子产品如何创新,结构体如何变化,材料如何更新,在进行结构分析时,所需要的力学学理,并没有太大的改变。当前的3D IC的TSV(Through Silicon Via)技术,其结构迥异于之前的IC封装结构,发展潜力无穷,但如果IC芯片运作所产生的热量没有办法适当的排除,电子构装不能解决IC芯片的废热问题,新开发的TSV就完全没有商业市场,由此可见电子构装技术的重要性。本文只是大致提到电子构装的结构分析的一些基本概念,并未涉入到诸多力学原理,抛砖引玉,期待国内电子构装先进更多深入的介绍,让国内更多的学生、工程师投入电子构装的研发领域。