2016年8月17日14:22

一 前言

材料学中将材料之间的结合面称为界面,比如有机物与有机物(DAF-EMC),有机物与无机非金属(Epoxy-Filler),有机物与金属(Cu Trace-Core),金属与无机非金属(Al Pad-IMD),金属与金属(Au-Al IMC),无机非金属与无机非金属(ILD-Poly)等等。而不同材料体系之间的结合就意味着不同的界面,也就会带来诸如污染,分层,腐蚀等材料学问题。界面通常是材料最薄弱的地方,是半导体器件最容易失效的地方,所以界面是做分析时重点关注的对象。。其实我们做失效分析,尤其是pFA,其目的就是要观察到失效的现象,推测失效原因(建立失效模型,验证失效机理),并反馈相关工程。与晶圆制造相比,封装的工艺相对简单,不过封装所用的材料体系更繁杂,界面种类也多,因此封装级别的失效相对复杂,但只要理清了分析的逻辑,问题也会迎刃而解。

二 样品制备

如前篇eFA(链接)所述,通过eFA分析已经可以大致推测出失效的类型或位置(I-V Curve判断失效位于基板还是芯片,Thermal获得热点即目标位置),接下来就要开始破坏性分析,也就是pFA。

样品制备是pFA的基础,一般为磨,抛,开封等。

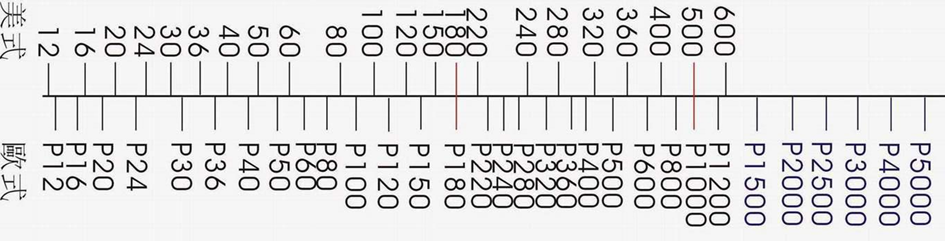

先说一下砂纸,一定要注意砂纸的编号,欧式的为P开头,而美式的不带P。下图给出了美式与欧式的对应关系,供参考。经验上看,国产的砂纸不耐磨,建议尽量用进口的,用不起美国的,用韩国的也行。

接下来介绍磨样,主要包括平磨和断面制备。平磨一般用于切线和多层芯片隔离。切线的目的是为了切断芯片与芯片或芯片与基板之间的电性连接,切线之后再次进行电性分析来确定失效位于哪一层。当已知失效位于哪层芯片后,就可以用热硝酸或RIE来开盖了。

制备一个好的断面需要耐心和技巧。精细断面制备一般要用树脂镶嵌之后再磨,而特别小的断面则要用聚焦离子束(FIB)来制备。较常用的镶样树脂有以下两种:1. 丙烯酸树脂,由粉体与液体两种组分混合后使用,固化速度快,15分钟就好,缺点是收缩率高,样品容易变形,填充性也差,镶好的样品里容易有气泡;2. 环氧树脂,固化时间较长,常温固化大于1小时,通常为两种液体混合,填充性好,收缩率低,形变小,若配合真空镶样机使用,基本可以消除气泡。磨断面的难点是既要保持样品的水平,又要保证最终的断面没有划痕且不能被污染。举例来说,磨一排Solder ball,首先要磨到球的直径位置,还要尽量做到一排球的断面都一样大。锡是一种很软的材料,要做到没有划痕,是要下一番功夫的。磨断面用的砂纸,抛光液,抛光布包括转速的选择都取决于要磨的材料和想要达到的效果,终抛一定要用抛光布+抛光液。如果只是粗略的看下断面,可以在样品上留一层水,在偏振光或暗场下,有些划痕会被掩盖,断面也会相对好看些。做精细断面制备,首先要对自己有信心,所谓熟能生巧,磨样的时候多总结经验教训,总归会越磨越好。(额外介绍一个亚克力树脂的小应用,用直径很小的细铜线,沾少许Flux,焊在器件背面的锡球或者焊盘上,然后滴几滴调好的亚克力树脂混合液,把焊点封好,利用引出的铜线可以在没有测试底座的情况下进行电测试,获得包括I-V Curve,Hotspot等重要信息)

开盖一般都用热硝酸与塑封料反应,而后用丙酮冲洗,温度有高有低。个人习惯将器件加热后滴硝酸进行Decap,当然也可以直接用硝酸煮。做高级FA有一项开盖技术是必须要掌握的,那就是Window Decap或者叫Partial Decap,即在器件表面滴开一个小窗口,只露出芯片的某个区域。Window Decap的技术要点是在Decap的过程中不能伤到基板与Solder ball,保留芯片与基板的连接,开盖之后还可以进行电性分析。

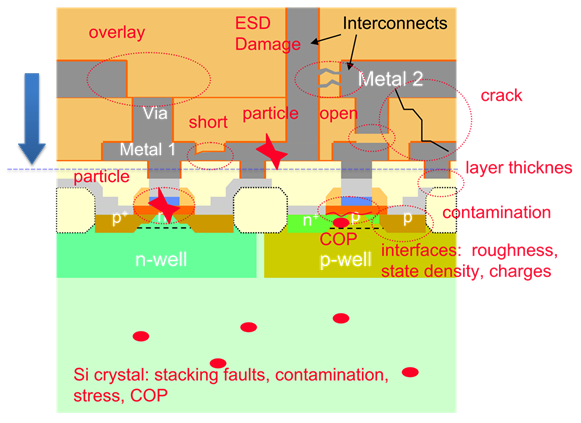

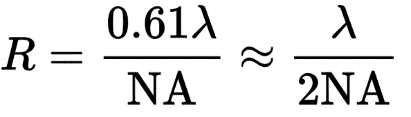

最后简单介绍一下封装级别分析不常用到的Delayer技术。从字面意思理解,Delayer就是剥层,真的要做Delayer的时候,基本就是到Die Level的级别了。由于保密或代工等原因,封测厂很少能拿到Layout,因此封测厂的FA其实只关注金属层以及Contact(W)即可,如下图中虚线往上的部分。

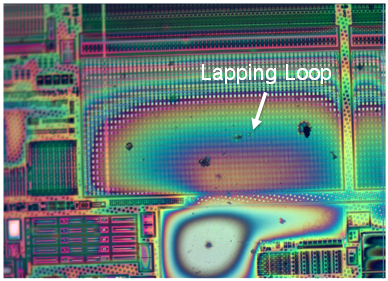

如果eFA可以给出确切的位置信息,包括Bitmap,以及Thermal,EMMI/InGaAs,OBIRCH等的热点,那么Delayer的成功率会得到很大提升。采用纯手抛或者用自动抛光机都可以实现Delayer,重点是要选择合适的抛光液和抛光布。抛光液可以选择微米或者纳米级的氧化铝或氧化硅悬浊液,也有厂家推荐使用金刚石悬浊液,而抛光布可以选择各厂家抛光液对应的那款抛光布。Delayer过程最关键是看Lapping Loop,不同的颜色代表不同的层,如下图所示[1]。

Delayer之前首先要确定目标位置,根据芯片上的Pattern或者用Laser Marking点做参照物,逐层剥(抛)下去。手抛很难做到整层的剥出,只要让Lapping Loop停在想要的那一层即可。其实大部分缺陷都位于金属层(两根相邻的Via之间,上下两层金属之间,Via或Metal底部),所以Delayer只要抛到目标金属层上的SiO2层,通过显微镜就能观察目标位置是否存在缺陷。如果不知道缺陷在哪一层,就只能针对热点位置逐层剥下去。到Contact之后还可以继续做Voltage Contrast,观察到异常点之后切FIB[2,3]。

反向工程[4]中用Delayer来复制版图,当然只是针对一些简单产品。一般的做法是逐层剥掉如SiNx,Metal,SiO2,Poly,AA等,并逐层拍照,获得版图。拍照主要针对金属层和Via层,而AA层还需要染色后才能区分出NMOS与PMOS。其实半导体技术早已经发展到让你抄无可抄的程度,例如Intel的14nm Tri-gate FinFET,剖面结构用TEM可以看的很清楚,但是谁也复刻不出来。再比如3D NAND,有做到64层的,有做到48层的,有做到32层的,互相之间也都了解彼此的工艺水平,也都会买别人家的产品来做反向工程,都想做更多层,但有些时候就是心有余而力不足。好吧,扯远了…

三 形貌观察

成像一般有两种模式:一种是采用外置激励源,如光,电子,离子,超声等,作用在样品上之后,收集反馈信号成像;另外一种是利用样品本身发出的信号来成像。FA常用的OM,SEM,SAT,X-ray都属于前者,Thermal和EMMI属于后者。前者又可分为两种模式,一种为反射像,一种为透射像。一般来说,反射都比透射清晰(TEM除外)。成像的效果主要与以下三点有关,衬度,景深和分辨率。关于显微成像的原理在网上有很多,在此不再赘述[5],以下重点介绍显微成像技术在失效分析中的应用以及不同成像技术之间的差别。首先谈谈日常分析中最常用的观察设备—光学显微镜。常见的光学显微镜附件有以下几个,

1. BF,明场,适合看平面

2. DF,暗场,适合看金属

3. PL,偏振,适合看有机薄膜

4. DIC,差分,适合看IMC

5. AS,孔径光阑,可以得到一定的景深,相当于小孔成像,孔径越小,景深越大

6. FS,视场光阑,可以缩小视场,不大常用

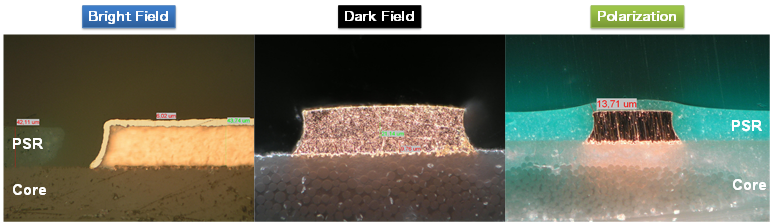

BF/DF/PL/DIC可以让显微镜输出不同的衬度,AS则可以略微改变成像的景深。其中偏振是非常重要的附件,因其有极佳的颜色衬度,特别是对不同种类的有机物可以呈现出不同的颜色,这是明场像,暗场像,甚或是SEM,包括EDX均无法实现的分辨能力。可以这样说,偏振附件对有机污染以及有机异物的观察在某些应用场合是不可替代的。举个例子,在偏振光下,PCB基板表面的绿漆是透明的淡绿色,这意味着不必去掉绿漆,就能看到绿漆下面铜布线的缺陷。暗场虽有类似的效果,但其亮度较低且颜色衬度较差,使其远没有达到偏振的清晰程度。下图给出了明场像,暗场像和偏振像之间的差别,仅供参考[6]。

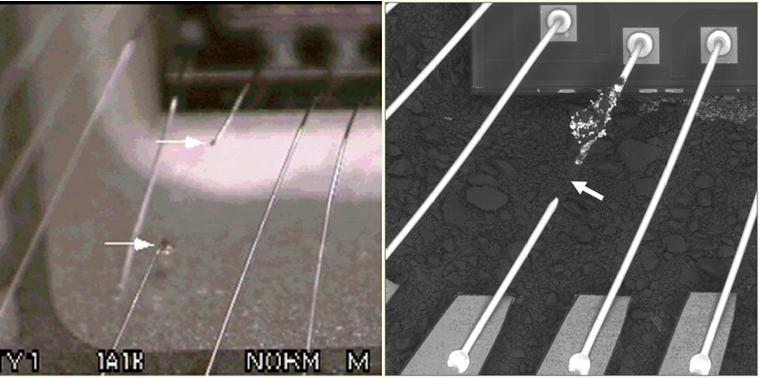

光学显微镜(OM)与电子显微镜(SEM)的区别在于,OM不仅有亮度衬度,还有颜色衬度,而SEM只有灰度衬度。但SEM的景深要比高倍显微镜的景深大得多,从下图可以看到OM与SEM在景深上的差别,左边为OM图像,右边为SEM图像。

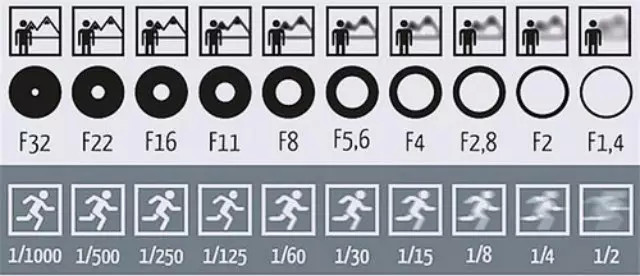

景深与放大倍数是矛盾的,镜头倍数越高,景深越浅,所以低倍显微镜的景深远大于高倍显微镜。在高倍率下调小孔径光阑,也能够获得一定的景深。下图很好的诠释了景深与光圈(AS)之间的关系,供参考。

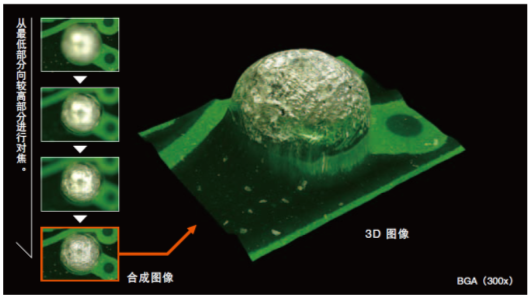

当然现在有3D显微镜,通过在不同焦平面拍照并在高度上进行叠加合成,可以在较高倍率下获得大景深,请见下图。

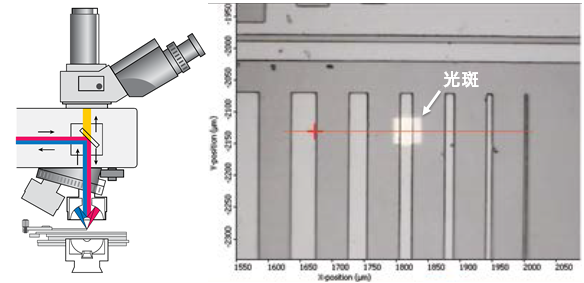

成像的分辨率可以参考下面这个公式,

其中R为可分辨的最小间距,也就是分辨率,λ为波长,NA为数值孔径。简单来说,波长越小,分辨率越高。比如,电子的波长远小于可见光的波长范围,因此SEM的分辨率要远高于光学显微镜,同时SEM的背散射探头还可以提供元素衬度像。再比如,红外线的波长比可见光要大,所以红外显微镜的分辨率比普通显微镜要差一些。同时,红外只有灰度图像,没有颜色衬度,不过某些波段的红外线在硅中的穿透率大于50%,因此可以穿过硅看到内部电路和缺陷。

综上所述,观察形貌时不应一味地追求高分辨率,选择能表现出缺陷或失效特征的最佳方法/手段才是最重要的。

四 异物&污染分析:

首先要分清异物和污染的概念。

1. 异物,英文是Foreign Material,即外来的物质。异物按材质可以分为金属,无机非金属和有机异物,按形状可以分为块状,颗粒,粉末,条状,丝状等。异物是封测厂较常见的不良,下表给出了封测厂常见异物的成分,形状及其可能来源。

异物会造成各种不良,如掉落在芯片表面,贴片的时候就可能造成Crack或Surface Damage。有时候Surface Damage很细微,如果Decap只去除DAF,则在Polymide表面可能会看到一个小洞,而去除Polymide之后,在Chip表面什么都看不到。有时候ESD也会在Polymide表面留下烧伤痕迹,而Decap以后却什么痕迹也没有。注意这个ESD Damage不一定在Pad附近,而可能出现在Chip表面任何位置,这也是一种新的放电模式,叫做ESDFOS(ESD from outside to surface[7])。硬质异物,比如硅碎屑,嵌在Wheel tooth里,会造成Wafer Scratch,粘在劈刀上,会造成临近的金线划伤。有时候一根丝状异物粘在涂Flux的Pin针上,则可能会引起Solder Bridge。

2. 污染,英文Contamination,通常为有机物,一般为薄薄的一层,有油脂状的,有表面变色的,有些甚至什么都看不出来。污染会导致分层,外观不合格,还有工程不良,比如BPT低或打不上线。

封装失效分析中常用的成分分析设备有两个,能谱(EDX)和傅里叶红外光谱(FT-IR)。能谱一般用于无机物分析,包括金属,氧化物,陶瓷,玻璃等。做能谱分析时要特别留意某些特征元素,比如钡Ba(PSR碎屑),氯Cl(诱发腐蚀),氟F(Polymide残留)等。X-ray Mapping是能谱附带的一个非常好用的工具,可以将不同元素用颜色区别标出,如下图。

X-ray Mapping可以将元素分布图像化,结果更为直观且易读,比较适合做Solder Bridge,Bump Extrusion,金属异物导致的Wire Short,Conductive Anodic Filaments(CAF)等金属化短路的表征。

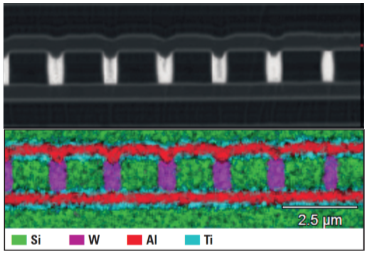

傅里叶红外光谱(FT-IR)则比较适合做有机异物或污染物分析。红外光谱的一个特点是附件众多,适用于不同状态的样品,液体,固态,薄膜,粉末等等。红外光谱为吸收谱,所以一定要穿过样品并扣除背景之后才能获得谱图。采集方式有以下四种,透射,衰减全反射(ATR),漫反射,镜面反射(Microscope)。下图为基于反射模式的显微红外光谱仪,通过调节如图的光斑来选区(ROI, region of interest),选区面积较小,特别适用于bonding Pad,Ball Land等光亮表面污染的分析。反射模式下样品越平、底面反光度越高,谱图质量就越好,这也很好理解,因为表面粗糙度越小,光线被散射的越少,被反射的也越多。当然显微红外还有透射模式,不过不常用。

显微红外有一个比较特殊的附件,Tip ATR Crystal,使用时装在显微镜的镜头上,如下图所示。Tip直径宜选择小的,可以戳在样品上,适合做Compound表面、PCB表面等相对较软的表面有机异物及污染物分析。Tip还可用于FT-IR Mapping,不过分辨率较差,用于分析的意义并不大。

有些情况下污染物较薄,薄到只有几个纳米的程度(浅表面),FT-IR和EDX都没法探测到或者说无法分辨出来,这时候可能要用XPS,Auger或者SIMS来分析。鉴于笔者对这几台设备不是很熟悉,以下表述,仅供参考[8]。

· XPS,光电子能谱仪,激发源为X射线,除了元素信息,还可以给出原子价键的信息,所以既可以做无机物分析,也可以做有机物分析

· AES,俄歇电子能谱,激发源为电子束,分辨率较高,适合分析导电性良好的样品,比如金属表面,但只能给出元素信息

· TOF-SIMS,飞行时间二次离子质谱仪,激发源是离子束,除了二次离子信息,还可以分辨有机物的官能团

XPS/Auger/TOF-SIMS,都可以做Profile,即可以测量污染物的厚度,这是EDX和FT-IR都没有的功能。不过EDX和FT-IR胜在价格便宜,解谱时也不需要太多材料或化学的知识背景,故实用性更高。

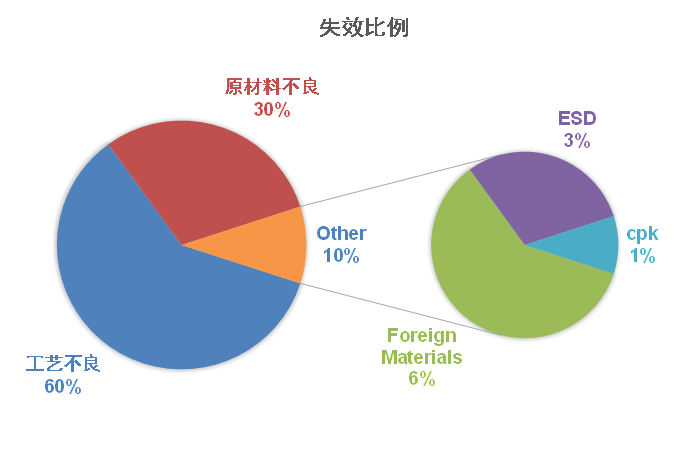

其实对于污染或异物,客户较关心的是会不会重复出现,是偶发的还是规律性的,而工艺工程师关心的是污染或异物的来源以及如何消除。所以分析异物或污染时除了要给出元素组成,更要考虑其物质组成和分子结构。一般来说,异物的分布是随机的,而污染则有一定集中性。分析污染时要根据现场的信息,判断其是否具有某种集中性(某条PCB,Wafer的某一区域,某一金型,某一lot等),并争取给出污染的来源,从而达到将其彻底消除的目的。异物的影响因素较多,比如某段时间产线施工,由异物引起的不良就会增多。与污染相比,异物的分析并不难,但其来源太杂,通常较难改善。异物之于产线就像灰尘之于空气一样,只能尽量减少,不能完全消除。而像产线的环境,洁净度等级,设备的摆放,PM的频率,气流的设计,载体(Tray盘,Magazine等)的清洗周期等都会影响到异物占总失效的比例。下图给出了封装失效分析中常见失效的比例,收率异常Lot的REJ一般源于工艺不良或者原材料不良,而收率正常Lot的REJ则能反映出产线的整体水平,包括cpk,异物分布,ESD管控水平等等。

五 结语与展望:

近年来,随着Flip-chip(倒装焊),RDL(再布线,包括WLP),尤其是基于深硅刻蚀TSV(第四代封装技术,硅通孔)与高深宽比MH(Memory Hole, 3D NAND)等技术的发展,工艺难度与日俱增,只有不断的开发并完善与之相匹配的失效分析和检测技术,才能持续提升这些先进工艺(包括晶圆制造与封装)的良率,降低成本,并最终实现量产。限于篇幅与知识背景,本文未能涵盖上述工艺的失效分析,但相信随着WLP,TSV以及3D NAND市场份额的增加,尤其是采用InFO封装工艺的iPhone7上市以及3D NAND普及之后,在未来一定会吸引更多对于失效分析与检测技术的关注[9]。